chip quântico com arquitetura crossbar promete concentrar milhões de qubits num espaço mínimo — já pensou no impacto disso na computação? Aqui eu explico, de forma direta e acessível, como a plataforma Qarpet funciona e por que ela pode acelerar prototipagem e testes de processadores semicondutores.

O que é a arquitetura crossbar (Qarpet) e por que importa

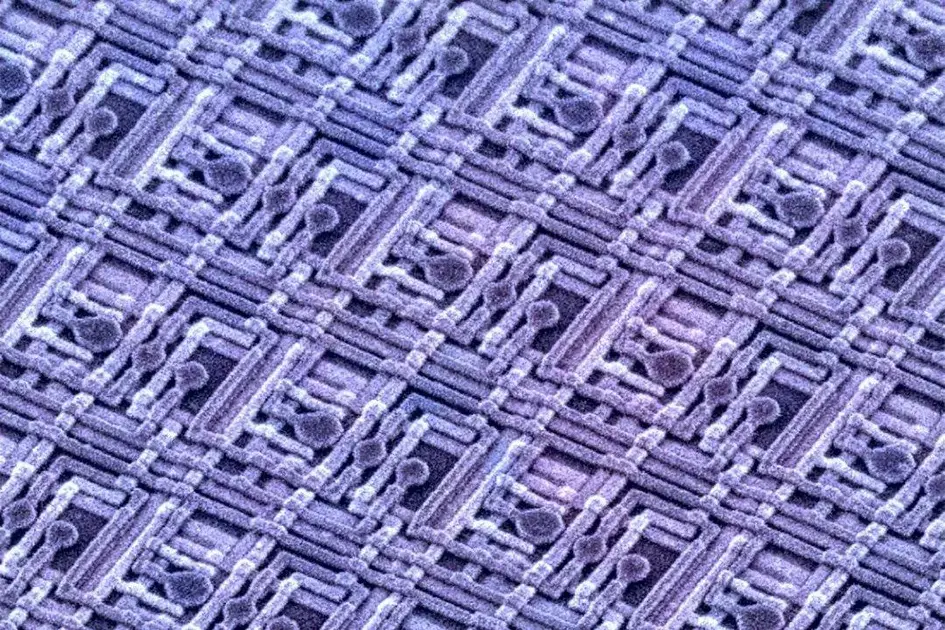

arquitetura crossbar é um esquema de interconexão que usa linhas cruzadas para controlar qubits. No projeto Qarpet, módulos repetidos formam uma grade tipo ladrilho. Cada módulo traz dois qubits e sensores de carga. Qubit é a unidade básica da computação quântica, como um bit, mas com superposição.

Como funciona na prática

Linhas metálicas cruzam-se em uma malha e tocam pontos de controle. Cada interseção pode endereçar um qubit específico. Sensores de carga lêem o estado dos qubits sem muitos fios. Esse desenho reduz a fiação e facilita testes rápidos.

Vantagens principais

A arquitetura permite alta densidade de qubits por área. Testes e prototipagem ficam mais simples e rápidos. O padrão em ladrilho facilita repetir módulos iguais. Isso ajuda a escalar chips e acelerar desenvolvimento.

Limites e desafios

Multiplexação e ruído são desafios comuns nesse esquema. Fabricar com precisão nanométrica exige processos avançados. Também é preciso gerenciar aquecimento e leitura sem interferir nos qubits. Pesquisas com Ge/SiGe mostram avanço, mas ainda há trabalho a fazer.

Como o protótipo Ge/SiGe organiza módulos com dois qubits e sensores

Ge/SiGe usa uma fina camada de germânio sobre silício-germânio. Essa junção melhora a mobilidade dos elétrons e torna os qubits mais estáveis em operação.

Estrutura dos módulos

Cada módulo abriga dois qubits próximos um do outro e eletrodos de controle. Um sensor de carga fica ao lado de cada par. Ele lê mudanças de carga sem contato direto.

Controle e leitura

Linhas metálicas cruzadas tocam os módulos para aplicar tensões em pontos específicos. Isso permite endereçar individualmente cada qubit sem fios extras demais. Os sensores usam multiplexação para ler muitos qubits com menos conexões. Multiplexação significa compartilhar canais de leitura sequencialmente para economizar fios e espaço.

Grade em ladrilho

Os módulos se repetem como ladrilhos numa malha regular. Cada ladrilho é idêntico, então a fabricação em série fica mais fácil. Esse padrão ajuda a escalar o chip para áreas maiores sem redesign complexo.

Benefícios para prototipagem

Ter módulos com dois qubits e sensores facilita testes rápidos de hardware novo. Equipes podem validar operações e medir fidelidade sem montar circuitos complexos. Isso reduz tempo e custo nas etapas iniciais de desenvolvimento.

Vantagens do esquema de barras cruzadas: controle, medição e escalabilidade

A arquitetura crossbar reduz bastante a quantidade de fios necessários no chip quântico. Menos conexões tornam o projeto mais simples e diminuem riscos de falha. Esse desenho facilita testes rápidos e acelera a prototipagem de chips.

Controle simplificado

Com barras cruzadas, você pode aplicar tensões em pontos bem específicos do chip. Isso permite endereçar qubits individualmente sem multiplicar os cabos de controle externos. O controle fica mais organizado e mais fácil de automatizar.

Medição eficiente

Sensores de carga leem mudanças de estado sem contato direto com os qubits. A leitura por multiplexação reduz o número de linhas necessárias no chip. Multiplexação significa compartilhar canais de leitura em sequência para economizar conexões.

Escalabilidade prática

O padrão em ladrilho permite repetir módulos idênticos em larga escala. Assim, os fabricantes podem aumentar densidade sem projetar cada parte do zero. A estratégia facilita testes de desempenho e acelera o desenvolvimento de processadores.

Principais ganhos

- Maior densidade de qubits por área reduz custo por qubit produzido em escala.

- Menor complexidade de fiação facilita manutenção e diagnóstico rápido de problemas.

- Padronização dos módulos reduz tempo de fabricação e custos de desenvolvimento.

Desafios técnicos e próximos passos para processadores quânticos maiores

chip quântico ainda enfrenta vários desafios técnicos antes de escalar para processadores maiores. Ruído e perda de coerência limitam o número de operações confiáveis por segundo.

Ruído e coerência

Reduzir ruído pede novos materiais, controles finos e proteção térmica e eletromagnética. Mais tempo de coerência torna as operações quânticas mais confiáveis e repetíveis.

Fiação e multiplexação

A arquitetura crossbar reduz fios, mas exige multiplexação e lógica de leitura sofisticada. Multiplexação, que é compartilhar linhas de leitura sequencialmente, economiza conexões, porém aumenta latência e complexidade.

Fabricação e controle

Fabricação precisa em escala exige alinhamento nanométrico e altos rendimentos de produção. Materiais como Ge/SiGe ajudam, mas os processos ainda precisam evoluir para maior uniformidade.

Eletrônica e criogenia

Controle eletrônico e criogenia também limitam a expansão para chips maiores. É preciso desenvolver circuitos de controle eficientes que funcionem em temperaturas muito baixas.

Próximos passos práticos

Próximos passos incluem padronizar módulos, testar em maior escala e integrar correção de erros. Mais colaboração entre universidades, indústrias e centros de fabricação vai acelerar soluções.